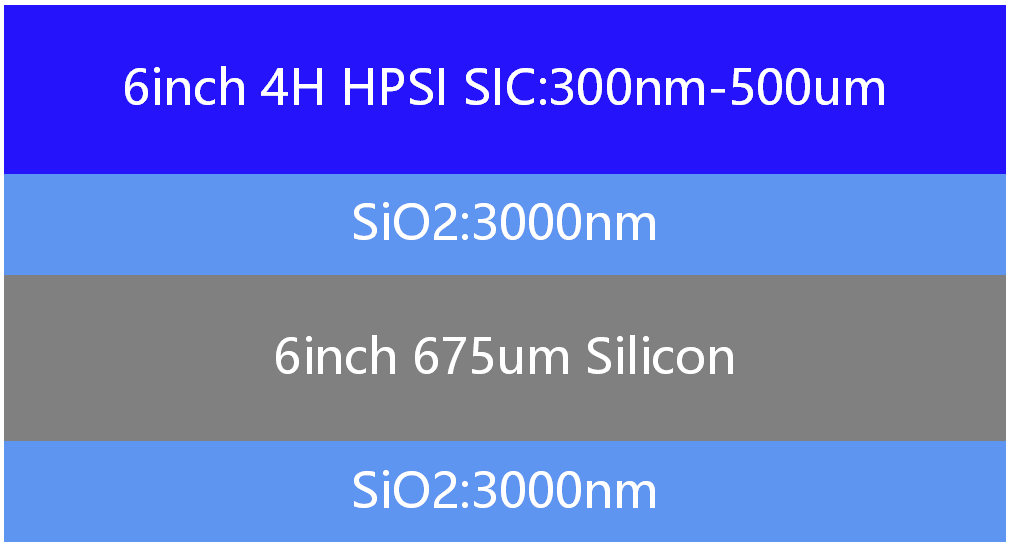

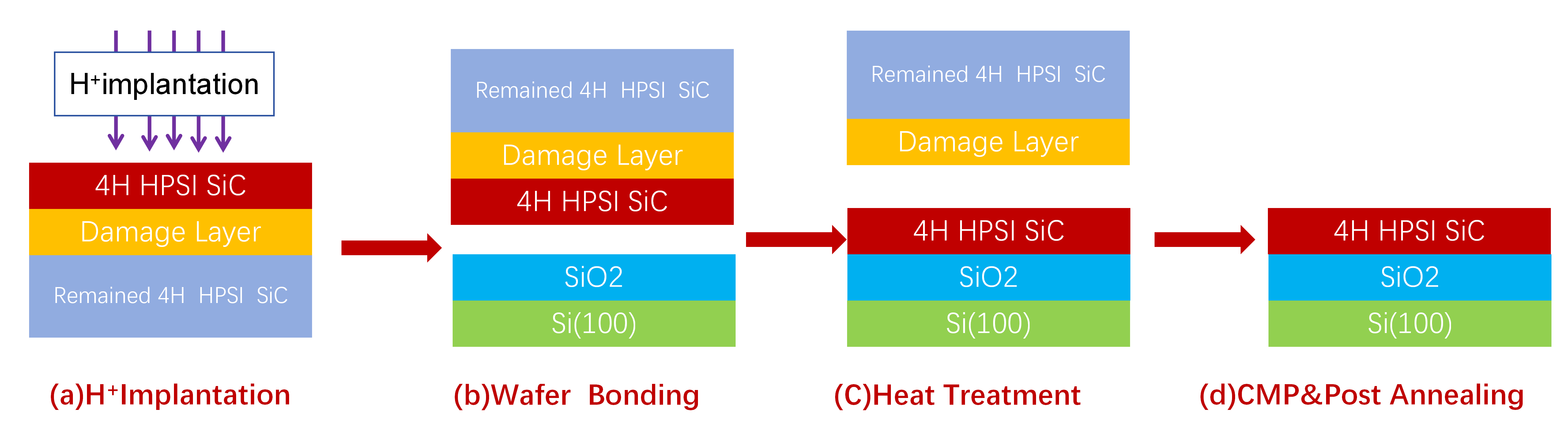

OMedaSemi develop 4-6 inch SICOI wafers (silicon carbide on insulator wafers). The wafers use Direct Bonding(hydropholic bonding) to bond thermal oxide wafers and 4H high-purity semi-insulating silicon carbide wafers together, and then control the thickness to the thickness you need through ion implantation, annealing, thinning or direct thinning and CMP polishing. ion implantation and direct CMP and thinning have their own advantages and disadvantages.

Optical Data we provide:Refractive Index and Absorption Data For Photonics integrated Circuit

Quantity that we shipped to Clients:20PCS

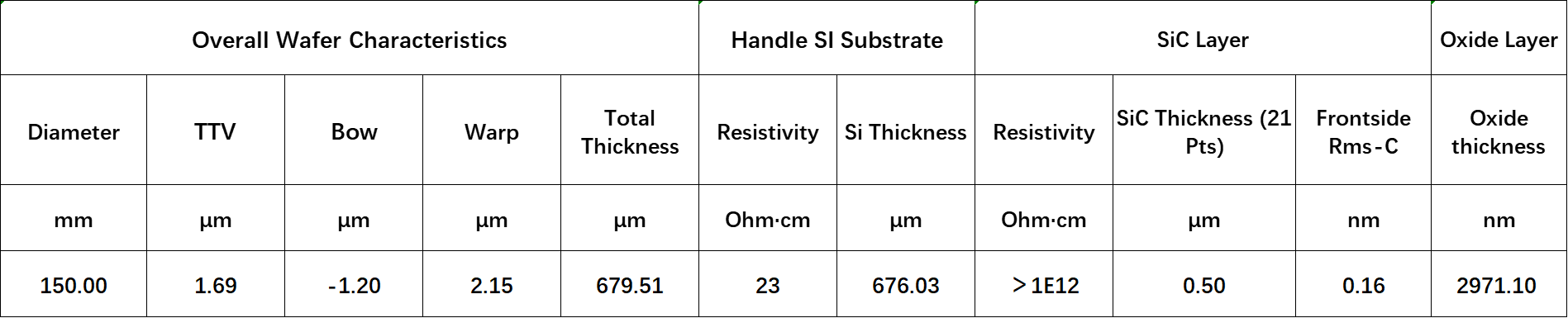

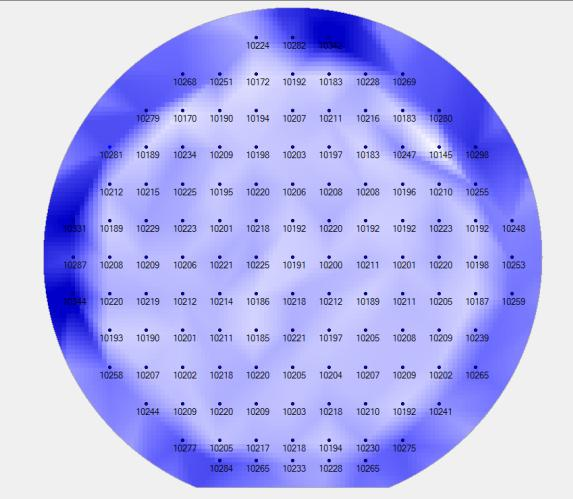

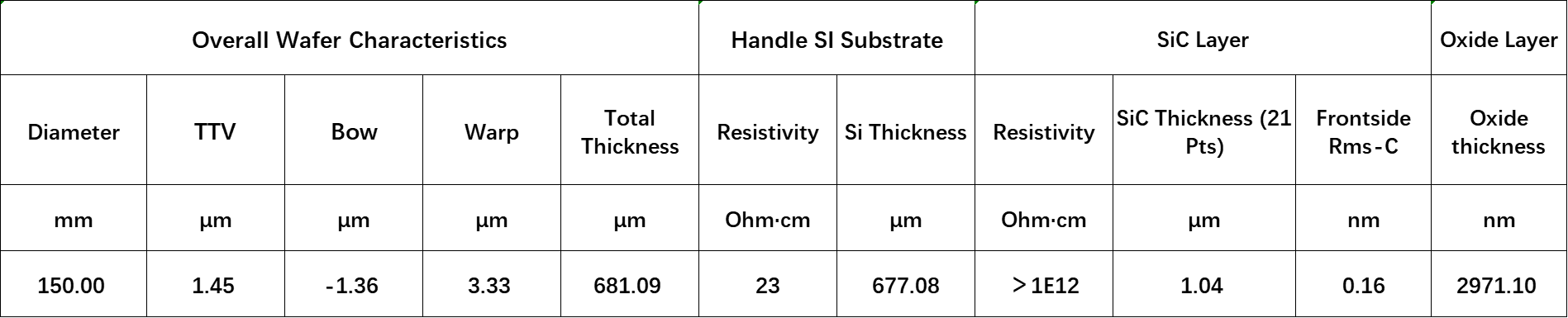

Data that we have ship to clients

Capbility

Based on SMARTCUT process, this method can provide good uniformity but bad optical performance so mainly for MEMS

Film thickness: 50nm-20um

Film thickness uniformity :+-20nm

Based on Grinding+CMP process,this method can provide not so good uniformity but good optical performance so mainly for Photonics and Quantum

Film thickness range: 200nm-any thickness

Film thickness uniformity: +-100nm

Optical Data for you to Simulation

Related paper:(Quantum Photonics MEMS)

Related paper:(MEMS)

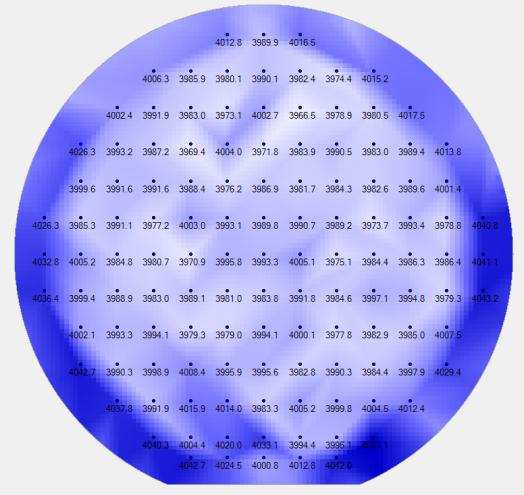

Test Data

Wafer 1:-400nm

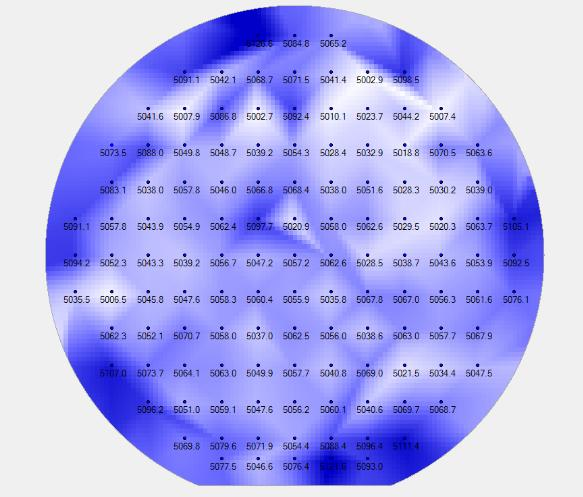

Wafer 2:-500nm

Wafer 2:-500nm

Wafer 3--1um

OMeda (Shanghai Omedasemi Co.,Ltd) was founded in 2021 by 3 doctors with more than 10 years of experience in nanpfabrication. It currently has 15 employees and has rich experience in nanofabrication (coating, lithography, etching, two-photon printing, bonding) and other processes. We support nanofabrication of 4/6/8-inch wafers.